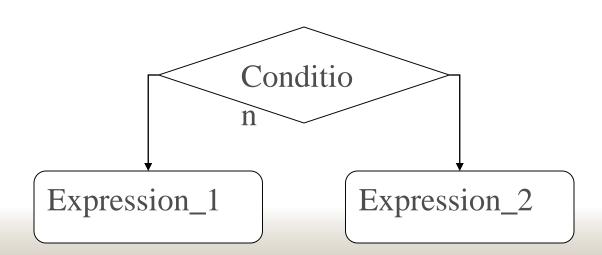

#### <u>Syntax:</u>

Signal name <= { expression 1 when condition else } expression 2;

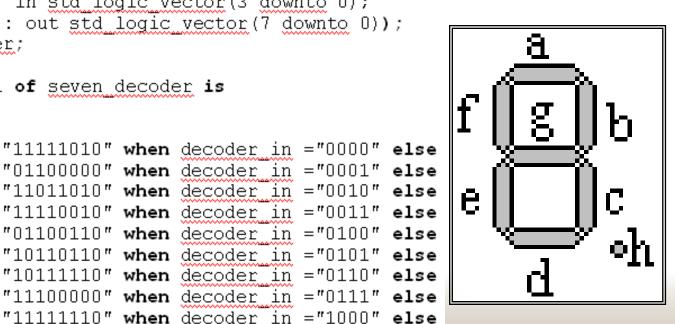

"11110110" when decoder in ="1001" else

```

use IEEE.STD LOGIC 1164.ALL;

entity seven decoder is

Port ( decoder in : in std logic vector(3 downto 0);

decoder out : out std logic vector(7 downto 0));

end entity seven decoder;

architecture Behavioral of seven decoder is

begin

decoder out <=

"11111010" when decoder in ="0000" else

"01100000" when decoder in ="0001" else

"11011010" when decoder in ="0010" else

"11110010" when decoder in ="0011" else

"01100110" when decoder in ="0100" else

"10110110" when decoder in ="0101" else

```

"00000000" :

### Example Multiple Driver

USE WORK.std\_logic\_1164.ALL; ENTITY mux IS

```

END mux;

ARCHITECTURE bad OF mux IS

BEGIN

```

```

q <= i0 WHEN a = '0' AND b = '0' ELSE '0';

q <= i1 WHEN a = '1' AND b = '0' ELSE '0';

q <= i2 WHEN a = '0' AND b = '1' ELSE '0';

q <= i3 WHEN a = '1' AND b = '1' ELSE '0';

END BAD;</pre>

```

# With...select

#### Syntax:

```

with selection signal select

signal name <= {

expression 1 when choice 1, }

expression 2 when choice 2,

expression n when choice n;

Condition_

Expression_1

Condition_

optio

Expression_2

Condition_

Expression_n

Expression_end

```

## Example

```

library IEEE;

clk sys

use IEEE.STD LOGIC 1164.ALL;

clk<u>2</u>

_{\rm clk\_3} \mid \rm Mux\, 4x1 \mid clk\_out

entity Mux4x1 is

clk n

Port ( clk sys : in std logic;

clk 2 : in std logic;

||Sel

clk 3 : in std legic;

clk n : in std logic;

Sel : in std logic vector(1 downto 0);

clk out : out std logic);

end entity Mux4x1;

architecture concurrent of Mux4x1 is

begin

```

end architecture concurrent;

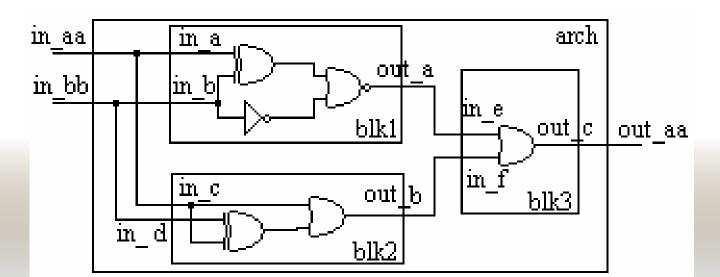

# ADIOGNA SIGNAMIA

#### Block Syntax:

label: **block**

block\_declarative domain;

begin

concurrent statements;

end block label ;

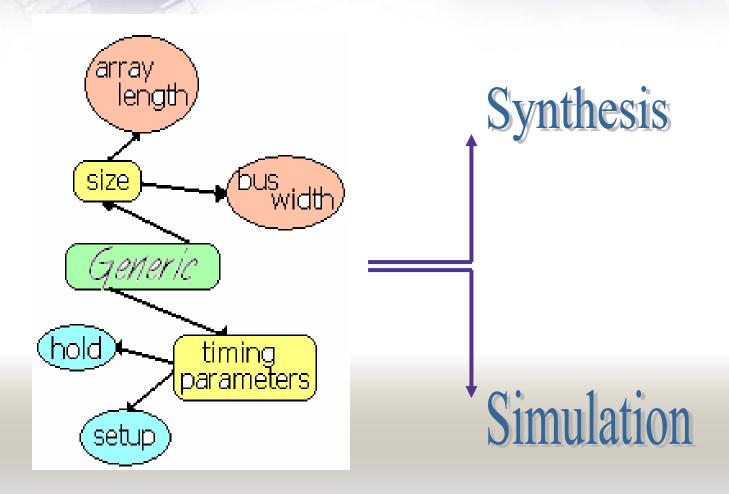

# AGENETIC STATEMENT

#### Syntax:

output

input