Examiner : Dr. Mustafa M. Shiple Subject: Shaping Circuits /(EEC 209)

Score: 30 Marks

Exam Time:60 min

## ANSWER THE FOLLOWING QUESTIONS:

1. Briefly discuss the following items

[10 marks ]  $[A_u, B_k]$

Term: Feb - May 2017

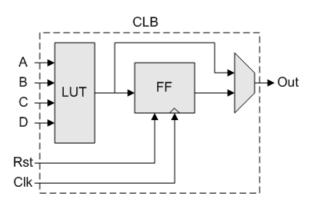

- (a) FPGA Architecture and sub-blocks

- (b) 6T Cell SRAM.

- (c) Metastability, Setup Time, Hold Time.

## **Solution:**

(a) PSM: Programmable Switch Matrices, responsible for connecting the different CLBs. CLB: Configurable Logic Block , responsible for accommodating the logic circuits that are required either asynchronously or asynchronously. IO Block: input/output blocks,responsible for dealing with i/o signals including timing issues and protection circuits

(b)

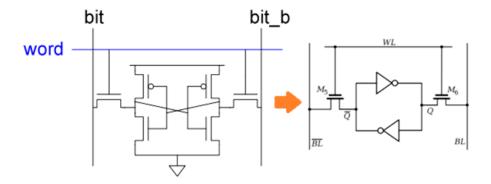

The structure of a 6 transistor SRAM cell, storing one bit of information, can be seen in Figure.

The access transistors and the word and bit lines, WL and BL, are used to read and write from or to the cell.

To write information the data is imposed on the bit line and the inverse data on the inverse bit line,  $\overline{BL}$ . Then the access transistors are turned on by setting the word line to high.

[Total Marks is 30]

Signature of Good Luck

Examiner: Head of Dept.:

page 1 of 4

For reading the word line is turned on to activate the access transistors while the information is sensed at the bit lines.

(c) Metastability:Result of violation of setup and hold times of a flip flop. Setup Time: The time required for data input to remain stable prior to arrival of clock pulse. Hold Time: The time required for data input to remain stable after the arrival of clock pulse.

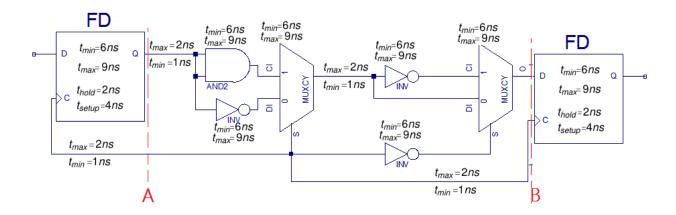

## 2. Calculate setup/hold violations

[6 marks ]  $[C_o, A_m]$

Signature of Examiner:

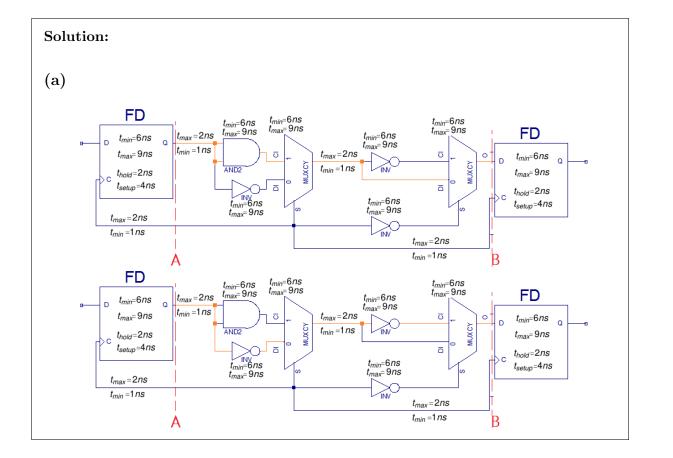

Good Luck Head of Dept.: There are two cases: 1) when S='1', 2)when S='0'.

• Case S='1':

```

\begin{aligned} Data\_Path(max) &= FD_{max} + path_{max} + AND_{max} + mux_{max} + path_{max} + mux_{max} + FD_{setup} \\ Data\_Path(max) &= 9 + 2 + 9 + 9 + 2 + 9 + 4 = 44ns \\ &clk\_Path(min) &= path_{min} + path_{min} + clk\_period \\ &clk\_Path(min) &= 1 + 1 + 15 = 17ns \\ & \therefore clk\_Path < Data\_Path \text{ by 27 (setup vaiolation)} \\ Data\_Path(min) &= FD_{min} + path_{min} + AND_{min} + mux_{min} + path_{min} + mux_{min} \\ Data\_Path(min) &= 6 + 1 + 6 + 6 + 1 + 6 = 26ns \\ &clk\_Path(max) &= path_{max} + path_{max} + FD_{hold} \\ &clk\_Path(max) &= 2 + 2 + 2 = 6ns \\ & \therefore clk\_Path < Data\_Path \text{ by 20ns (no hold vaiolation)} \end{aligned}

```

• Case S='0':

```

\begin{aligned} Data\_Path(max) &= FD_{max} + path_{max} + INV_{max} + mux_{max} + path_{max} + INV_{max} + mux_{max} + FD_{setup} \\ Data\_Path(max) &= 9 + 2 + 9 + 9 + 2 + 9 + 9 + 4 = 53ns \\ &clk\_Path(min) &= path_{min} + path_{min} + clk\_period \\ &clk\_Path(min) &= 1 + 1 + 15 = 17ns \\ & \therefore clk\_Path < Data\_Path \text{ by 36ns (setup vaiolation)} \\ Data\_Path(min) &= FD_{min} + path_{min} + gate_{min} + mux_{min} + path_{min} + mux_{min} \\ Data\_Path(min) &= 6 + 1 + 6 + 6 + 1 + 6 + 6 = 32ns \\ &clk\_Path(max) &= path_{max} + path_{max} + FD_{hold} \\ &clk\_Path(max) &= 2 + 2 + 2 = 6ns \end{aligned}

```

From the above analysis the maximum setup violation is 36ns and no hold violation. Therefore, the proposed solution is to add the violation time to clock period to be 15+36=51 ns that means the maximum frequency will be reduced to be  $\frac{1}{51n} = 19.6 GHz$

:. clk\_Path < Data\_Path by 26 (no hold vaiolation)

3. Write a VHDL code that realizes the previous circuit which is bounded by dashed lines A,B.(Hint: make the width of S generic input) [10 marks]  $[B_k, C_o, A_m]$

```

Solution:

entity MT209 is

```

Signature of Good Luck

Examiner: Head of Dept.:

```

Generic (width: integer :=0);

port( S:in std_logic_vector(width downto 0);

A:in std_logic;

B:out std_logic);

end MT209;

architecture Behavioral of MT209 is

begin

B <= not(A) when S="1" else (A and A) when S="0" else (A and A) when S="1" else not(A);

end Behavioral;</pre>

```

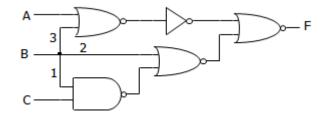

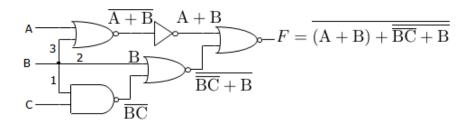

4. Evaluate the next circuit against glitches, resolve hazards if existed.

[4 marks]  $[A_d, A_q]$

**Solution:** General rules:

- 1- No for Distributive Law.

- 2- OK for DeMorgan Law.

$$3-F = \overline{(A+B)} + \overline{\overline{BC} + B}$$

4-simplify without using Distributive Law. $F = \overline{B} \cdot \overline{A} \cdot (\overline{BC} + B)$

- 5-Dynamic @  $A = 0, C = 1 \Rightarrow \overline{B} \cdot (\overline{B} + B)$

- 6-The circuit could be resolved by synchronous systems.