# **Introduction to Assembly (8085)**

Dr. M. Shiple

Microprocessor Architecture, 2019

# **Assembly Sections**

# **Assembly Sections**

labels: takes the address of instruction. For example, start= address of "nop" instruction.

```

; < Program title>

3

jmp start

4

5

:data

6

Declaration section

8

; code

9

start: nop

10

11

Code section

12

hlt

13

To stop the execution

```

# **Addressing Modes in 8085**

## Register mode

An operand may be in:

- Accumulator A.

- Memory

- Device control registers

# **Register Addressing Mode:**

The data is copied from one register to another.

The data to be operated is available inside registers (the operands are registers).

- MOV A,B ;A=B

- ② ADD B ;A=A+B

- INR A ;A=A+1

#### Immediate mode

### Immediate addressing mode:

The 8/16-bit data is specified in the instruction itself as one of its operand.

The source operand is always data.

● MVI B,45 :B=45

2 LXI H,3050h ;(load the H-L pair with 3050H immediately)

3 JMP 0x2030 ;(jump to the operand address immediately)

#### **Direct Mode**

### **Direct addressing mode**

The data is directly copied from the given address to the register.

The data to be operated is available inside a memory location and that memory location is directly specified as an operand.

LDA 2050 ;A=[2050h]

② LHLD 2030 ;HL=[2030h]

3 IN 80 ;A=[port B]

#### **Indirect Mode**

## Indirect addressing mode

The data is transferred from one register to another by using the address pointed by the register.

The data to be operated is available inside a memory location and that memory location is indirectly specified b a register pair.

🚺 MOV A, M

;A=[[HL]]

# **Instruction set**

#### **Definitions**

#### Instruction:

a binary pattern designed inside a microprocessor to perform a specific function.

- 8085 has 246 instructions.

- Each instruction is represented by an 8-bit binary value.

- These 8-bits of binary value is called Op-Code (machine language) or Instruction Byte/mnemonics (Assembly).

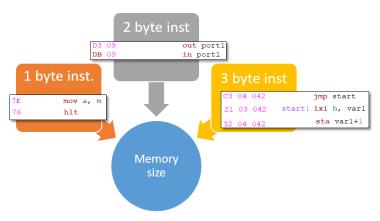

#### **Instruction Word Size**

#### Instruction:

a binary pattern designed inside a microprocessor to perform a specific function.

### Instruction set

\*operation code: (often abbreviated to opcode)

### **Instruction set: Data transfer (Mov)**

| Instructions |           | Onenetien | Cualaa | Bytes | Flag | Decemention               |  |

|--------------|-----------|-----------|--------|-------|------|---------------------------|--|

| Mnemonics    | Arguments | Operation | Cycles | bytes | Flag | Description               |  |

| MOV          | r1,r2     | r1=r2     | 4      | 1     |      | Move register to register |  |

| MOV          | M,r       | [HL]=r    | 7      | 1     |      | Move register to Memory   |  |

| MOV          | r,M       | r=[HL]    | 7      | 1     |      | Move Memory to register   |  |

| MVI          | r,n       | r=n       | 7      | 2     |      | Move Immediate            |  |

| MVI          | M,n       | [HL]=n    | 10     | 2     |      | Move Immediate to Memory  |  |

# **Instruction set: Data transfer (Mov)**

[p]=A

EPUZ01

р

| Instructions |           | Onenstian | Cualas | Durtos | Floor | Description                |

|--------------|-----------|-----------|--------|--------|-------|----------------------------|

| Mnemonics    | Arguments | Operation | Cycles | Bytes  | Flag  | Description                |

| LDA          | a         | A=[a]     | 13     | 3      |       | Load Accumulator direct    |

| LDAX         | В         | A=[BC]    | 7      | 1      |       | Load Accumulator indirect  |

| LDAX         | D         | A=[DE]    | 7      | 1      |       | Load Accumulator indirect  |

| LHLD         | а         | HL=[a]    | 16     | 3      |       | Load HL Direct             |

| LXI          | B,nn      | BC=nn     | 10     | 3      |       | Load Immediate BC          |

| LXI          | D,nn      | DE=nn     | 10     | 3      |       | Load Immediate DE          |

| LXI          | H,nn      | HL=nn     | 10     | 3      |       | Load Immediate HL          |

| LXI          | SP,nn     | SP=nn     | 10     | 3      |       | Load Immediate Stack Ptr   |

|              |           |           |        |        |       |                            |

| STA          | а         | [a]=A     | 13     | 3      |       | Store Accumulator          |

| STAX         | В         | [BC]=A    | 7      | 1      |       | Store Accumulator indirect |

| STAX         | D         | [DE]=A    | 7      | 1      |       | Store Accumulator indirect |

|              |           |           |        |        |       |                            |

| SHLD         | а         | [a]=HL    | 16     | 3      |       | Store HL Direct            |

| SPHL         |           | SP=HL     | 6      | 1      |       | Move HL to SP              |

| XCHG         |           | HL<->DE   | 4      | 1      |       | Exchange HL with DE        |

| XTHL         |           | [SP]<->HL | 16     | 1      |       | Exchange stack Top with HL |

|              |           |           |        |        |       |                            |

| IN           | р         | A=[p]     | 10     | 2      |       | Input                      |

http://Drshiple-courses.weebly.com/put

# **Instruction set: Data transfer (Mov)**

[p]=A

EEUZ01

р

| Instructions |           | <u> </u>  |        | Б.    |      | B                          |  |

|--------------|-----------|-----------|--------|-------|------|----------------------------|--|

| Mnemonics    | Arguments | Operation | Cycles | Bytes | Flag | Description                |  |

| LDA          | a         | A=[a]     | 13     | 3     |      | Load Accumulator direct    |  |

| LDAX         | В         | A=[BC]    | 7      | 1     |      | Load Accumulator indirect  |  |

| LDAX         | D         | A=[DE]    | 7      | 1     |      | Load Accumulator indirect  |  |

| LHLD         | а         | HL=[a]    | 16     | 3     |      | Load HL Direct             |  |

| LXI          | B,nn      | BC=nn     | 10     | 3     |      | Load Immediate BC          |  |

| LXI          | D,nn      | DE=nn     | 10     | 3     |      | Load Immediate DE          |  |

| LXI          | H,nn      | HL=nn     | 10     | 3     |      | Load Immediate HL          |  |

| LXI          | SP,nn     | SP=nn     | 10     | 3     |      | Load Immediate Stack Ptr   |  |

|              |           |           |        |       | •    |                            |  |

| STA          | а         | [a]=A     | 13     | 3     |      | Store Accumulator          |  |

| STAX         | В         | [BC]=A    | 7      | 1     |      | Store Accumulator indirect |  |

| STAX         | D         | [DE]=A    | 7      | 1     |      | Store Accumulator indirect |  |

|              |           |           |        |       |      |                            |  |

| SHLD         | а         | [a]=HL    | 16     | 3     |      | Store HL Direct            |  |

| SPHL         |           | SP=HL     | 6      | 1     |      | Move HL to SP              |  |

| XCHG         |           | HL<->DE   | 4      | 1     |      | Exchange HL with DE        |  |

| XTHL         |           | [SP]<->HL | 16     | 1     |      | Exchange stack Top with HL |  |

|              |           |           |        |       |      |                            |  |

| IN           | р         | A=[p]     | 10     | 2     |      | Input                      |  |

http://Drshiple-courses.weebly.com/put

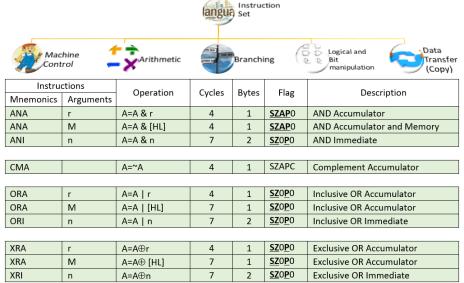

## Instruction set: Bit manupilation

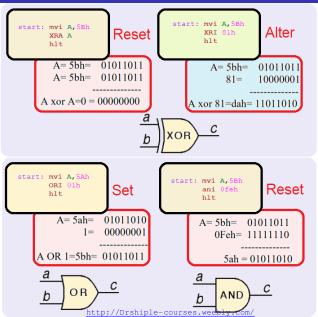

# Instruction set: Bit manupilation (Examples:CMA)

$$A=5Ah=$$

01011010

$A=A5h=$  10100101

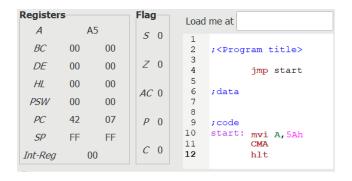

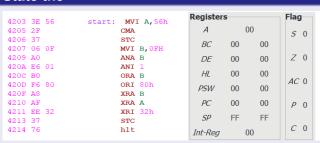

# **Instruction set: Bit manupilation (Examples:XOR)**

```

Registers

Flag

Load me at

Α

45

5 0

BC

1F

00

; < Program title>

3

Z = 0

00

DE

00

imp start

5

HL

00

00

;data

AC 0

PSW

00

00

PC

42

09

P = 0

; code

10

start: mvi A,5Ah

SP

FF

FF

11

mvi B, 1Fh

C

0

12

Int-Reg

00

XRA B

13

hlt

```

# Instruction set: Bit manupilation (Examples:Masking)

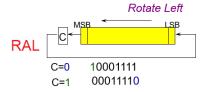

# **Instruction set: Bit manupilation (Rotation)**

| Instructions |           | Operation  | Cycles | Bytes | Flog          | Description              |

|--------------|-----------|------------|--------|-------|---------------|--------------------------|

| Mnemonics    | Arguments | Operation  | Cycles | bytes | Flag          | Description              |

| RAL          |           | A={CY,A}<- | 4      | 1     | SZAP <u>C</u> | Rotate Accumulator Left  |

| RAR          |           | A=->{CY,A} | 4      | 1     | SZAP <u>C</u> | Rotate Accumulator Right |

| RLC | A=A<- | 4 | 1 | SZAP <u>C</u> | Rotate Left Circular  |

|-----|-------|---|---|---------------|-----------------------|

| RRC | A=->A | 4 | 1 | SZAP <u>C</u> | Rotate Right Circular |

# Instruction set: Bit manupilation (Non distructive)

| Instructions |           | Operation | Cycles | Bytes | Flag                      | Description       |

|--------------|-----------|-----------|--------|-------|---------------------------|-------------------|

| Mnemonics    | Arguments | Operation | Cycles | bytes | Flag                      | Description       |

| CMP          | r         | A-r       | 4      | 1     | SZAPC                     | Compare           |

| CMP          | М         | A-[HL]    | 7      | 1     | SZAPC Compare with Memory |                   |

| CPI          | n         | A-n       | 7      | 2     | SZAPC                     | Compare Immediate |

### CMP is a non-destructive compare

- Sets ZF and CF as appropriate.

- Does not change either of the operands.

#### Instruction set: Excersize

### Write programs with effects?

HL= (BC+HL) OR DE (use register pair when necessary), when BC=105h, HL=340h, DE=180h

## Change bit patteren as?

Reset bits 0,2 of A and set bits 4,6,7 when A=0A7H

## State the

Memory Size?

**Processing Time?**

### **Instruction set: Branching**

#### Instruction set: Function call

| Instructions |           | Operation     | Cvcles   | Bytes | Flag  |                     |

|--------------|-----------|---------------|----------|-------|-------|---------------------|

| Mnemonics    | Arguments | Орегаціон     | Cycles   | bytes | 1 lag | Description         |

| CALL         | a         | -[SP]=PC,PC=a | 18       | 3     |       | Call unconditional  |

| CM           | а         | If S=1        | 9/(18~s) | 3     |       | Call on Minus       |

| СР           | а         | If S=0        | 9/(18~s) | 3     |       | Call on Plus        |

| CC           | а         | If CY=1       | 9/(18~s) | 3     |       | Call on Carry       |

| CNC          | а         | If CY=0       | 9/(18~s) | 3     |       | Call on No Carry    |

| CZ           | а         | If Z=1        | 9/(18~s) | 3     |       | Call on Zero        |

| CNZ          | а         | If Z=0        | 9/(18~s) | 3     |       | Call on No Zero     |

| CPE          | а         | If P=1        | 9/(18~s) | 3     |       | Call on Parity Even |

| СРО          | а         | If P=0        | 9/(18~s) | 3     |       | Call on Parity Odd  |

Before the transfer, the address of the next instruction after the call (the contents of the program counter) is pushed onto the stack.

#### **Instruction set: Function Return**

| Instructions |           | Operation | Cvcles   | D. 4  |      |                       |

|--------------|-----------|-----------|----------|-------|------|-----------------------|

| Mnemonics    | Arguments | Operation | Cycles   | Bytes | Flag | Description           |

| RET          |           | PC=[SP]+  | 10       | 1     |      | Return                |

| RM           |           | If S=1    | 6/(12~s) | 1     |      | Return on Minus       |

| RP           |           | If S=0    | 6/(12~s) | 1     |      | Return on Plus        |

| RC           |           | If CY=1   | 6/(12~s) | 1     |      | Return on Carry       |

| RNC          |           | If CY=0   | 6/(12~s) | 1     |      | Return on No Carry    |

| RZ           |           | If Z=1    | 6/(12~s) | 1     |      | Return on Zero        |

| RNZ          |           | If Z=0    | 6/(12~s) | 1     |      | Return on No Zero     |

| RPE          |           | If P=1    | 6/(12~s) | 1     |      | Return on Parity Even |

| RPO          |           | If P=0    | 6/(12~s) | 1     |      | Return on Parity Odd  |

The two bytes from the top of the stack are copied into the program counter, and program execution begins at the new address.

### **Instruction set: Function Return**

| Instructions |           | Operation     | Cycles | Durtos | Flag         | Description              |

|--------------|-----------|---------------|--------|--------|--------------|--------------------------|

| Mnemonics    | Arguments | Operation     | Cycles | Bytes  | riag         | Description              |

| ACI          | n         | A=A+n+CY      | 7      | 2      | <u>SZAPC</u> | Add with Carry Immediate |

| ADC          | r         | A=A+r+CY(21X) | 4      | 1      | <u>SZAPC</u> | Add with Carry           |

| ADC          | М         | A=A+[HL]+CY   | 7      | 1      | <u>SZAPC</u> | Add with Carry to Memory |

| ADD          | r         | A=A+r (20X)   | 4      | 1      | <u>SZAPC</u> | Add                      |

| ADD          | М         | A=A+[HL]      | 7      | 1      | <u>SZAPC</u> | Add to Memory            |

| ADI          | n         | A=A+n         | 7      | 2      | <u>SZAPC</u> | Add Immediate            |

| DAD | В  | HL=HL+BC | 10 | 1 | SZAP <u>C</u> | Double Add BC to HL |

|-----|----|----------|----|---|---------------|---------------------|

| DAD | D  | HL=HL+DE | 10 | 1 | SZAP <u>C</u> | Double Add DE to HL |

| DAD | Н  | HL=HL+HL | 10 | 1 | SZAP <u>C</u> | Double Add HL to HL |

| DAD | SP | HL=HL+SP | 10 | 1 | SZAP <u>C</u> | Double Add SP to HL |

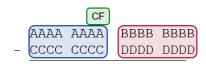

### Instruction set: Multi-byte Addition and Subtraction

- 1. ADD B + D (carry out in CF)

- 2. ADD A + C + CF

- 1. SUB B D (borrow in CF)

- 2. SUB A C CF