Examiner : Dr. Mustafa M. Shiple Subject: Selected Topics in Electronics /(ECE 569) Score: 5 Marks

## ANSWER THE FOLLOWING QUESTIONS:

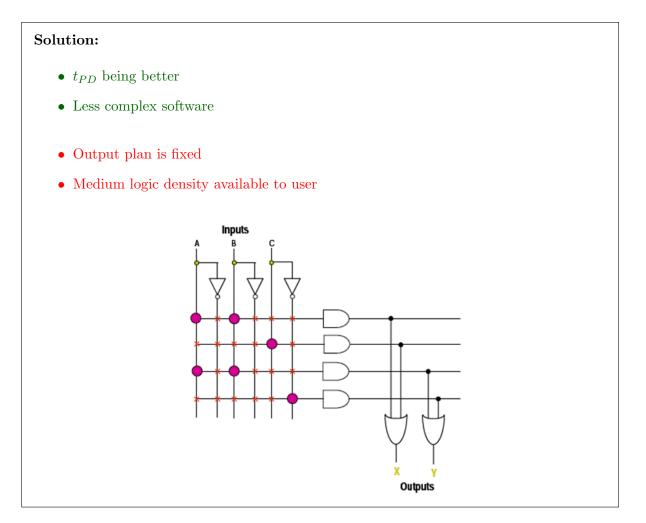

1. Briefly discuss pros and cons of single PAL

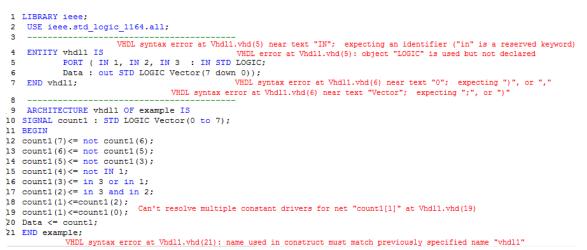

- 2. Consider the next VHDL code:

- (a) Check and correct syntax errors.

- (b) Synthesize the next code, and Draw the circuit.

```

LIBRARY ieee;

1

USE ieee.std_logic_6411.all;

\mathbf{2}

3

ENTITY freq IS

4

PORT (IN 1, IN 2, IN 3 : IN STD LOGIC;

5

Data : out STD LOGIC Vector (7 \text{ down } 0);

6

END freq;

7

8

ARCHITECTURE freq OF example IS

9

SIGNAL count1 : STD LOGIC Vector (0 to 7);

10

BEGIN

11

```

[Total Marks is 5]

```

\operatorname{count1}(7) \leq \operatorname{not} \operatorname{count1}(6);

12

\operatorname{count1}(6) \leq \operatorname{not} \operatorname{count1}(5);

13

\operatorname{count1}(5) \leq \operatorname{not} \operatorname{count1}(3);

14

\operatorname{count1}(4) \ll \operatorname{not} \operatorname{IN} 1;

15

\operatorname{count1}(3) \leq \operatorname{in} 3 \text{ or in } 1;

16

\operatorname{count1}(2) \le \operatorname{in} 3 and \operatorname{in} 2;

17

\operatorname{count1}(1) \leq \operatorname{count1}(2);

18

\operatorname{count1}(1) \leq \operatorname{count1}(0);

19

Data \leq = \text{count1};

20

END example;

21

22

```

## Solution:

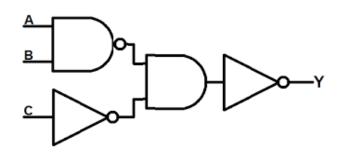

3. Write a VHDL entity code that realizes the shown circuit.

## Solution:

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

```

```

ENTITY vhdl1 IS

PORT ( a, b, c : IN STD_LOGIC;

y : out STD_logic);

END vhdl1;

ARCHITECTURE example OF vhdl1 IS

SIGNAL nand_out , and_out : STD_logic;

10

BEGIN

11

12

nand_out <= a nand b;

and_out <= nand_out and not c;

13

y \le not and_out;

14

15

END example;

16

17

```